eFPGA IP Cores v5

Menta eFPGAs are high-density embedded programmable logic IPs for use in SoCs or ASICs. They are designed to address various markets and applications. Menta eFPGA IP cores empower designers to define the specific resources required for their applications needs. Available as Soft RTL or Hard GDSII IP.

Why embedded FPGA?

Secrets protection

With Menta eFPGA you can wait to

deliver your most proprietary technology

to end-customers as a field-upgrade,

minimizing any opportunity for

competitors to reverse engineer your

product.

Higher performance

With Menta eFPGA, sacrifices in board-space, I/O latency, and bandwidth disappear, as you bring those accelerators on-chip, without the limitations/overhead due I/O padcount or chip-to-chip communication interfaces.

Design insurance

Maximizing flexibility requires maximizing process-portability. Menta eFPGA is the only 100% standard-cell based solution and this approach enables rapidly porting your eFPGA to whatever new process geometry/variant you desire, using the same automated, standard EDA flow as for the rest of your SoC. Menta, using our industry gold-standard Synopsys-based implementation flow, enables portability within just weeks.

Secrets protection

At higher production volumes, onboard FPGAs quickly become cost prohibitive. With Menta eFPGA you integrate on-board FPGA functionality on-chip, saving manufacturing costs and board-space, while fully maintaining field-upgradability.

Lower power consumption

In a COT FPGA, all the extra to the programmable logic, such as high-speed interfaces, PLL, and controllers consume around half of the power. All our power saving advances lead an algorithm on a Menta eFPGA IP to consume between 10 and 50% of the power of the same algorithm on a FPGA.

Security

In today’s global, multi-player design-chain, preserving IP/trade secrets is more critical and challenging than ever. With Menta eFPGA you can wait to deliver your most proprietary technology to end-customers as a field-upgrade, minimizing any opportunity for competitors to reverse engineer your product.

Menta eFPGA IP differentiators

Menta is committed to maximizing process portability, so our eFPGAs have been silicon-proven on more technology nodes than any other eFPGA vendor. Menta supports any CMOS foundry and node from 350nm to 5nm or less. To date, Menta eFPGAs have been successfully manufactured on technologies as diverse as: STM130, STM65, TSMC 28HPC+, TSMC 12FFC and GLOBALFOUNDRIES 12LP. Menta eFPGAs are qualified on GLOBALFOUNDRIES® 32 SOI and 14LPP. Menta is also a 22 FDXceleratorTM Partner. Menta IPs are currently being delivered on XFAB 180nm, STM28 FDSOI and others.

Unparalleled process-portability

Menta eFPGA is the only 100% standard-cell based solution. Menta’s standard-cell based approach enables rapidly porting your eFPGA to whatever new process geometry/variant you desire, using the same automated, standard EDA flow as for the rest of your SoC.

Design Adaptive

Menta allows customers to specify the number of embedded Logic blocks (eLBs), number/type of DSPs, RAMs, number/type of interconnects, as well as different power-saving features. Menta offers designers a variety of DSP-arithmetic logic blocks to incorporate within its eFPGAs, and continued to expansion based on customer requirements.

Easy to integrate

Menta designed its eFPGA so that it can be verified at various levels: using formal verification for mapped applications, system simulation with SDF timing information, and even gate-level simulation post place-and-route. Bitstream loading can be simulated and verified as well. We call it Trusted eFPGA.

Cost

At higher production volumes, on-board FPGAs quickly become cost-prohibitive. With Menta eFPGA you integrate on-board FPGA functionality on-chip, saving manufacturing costs and board-space, while fully maintaining field-upgradability. Similarly, if your company in the past has relied on SoCs, Menta eFPGA enables you to minimize the number of chip-variants, time-to-market, and dynamically adapt to evolving standards.

Robustness

At Menta, we believe that different problems require different solutions. Therefore, our customers can define the exact resources required for their application.

Programming Software

Menta created this specially “targeted” programming software-tool to generate the bitstream that targets/optimizes your RTL specifically to the Menta eFPGA architecture. Menta does not rely on 3rd party software tools which target “generic” FPGA architectures, thus delivering suboptimal results. Menta’s independent software development frees Origami Programmer from any export-control and patent litigation issues.

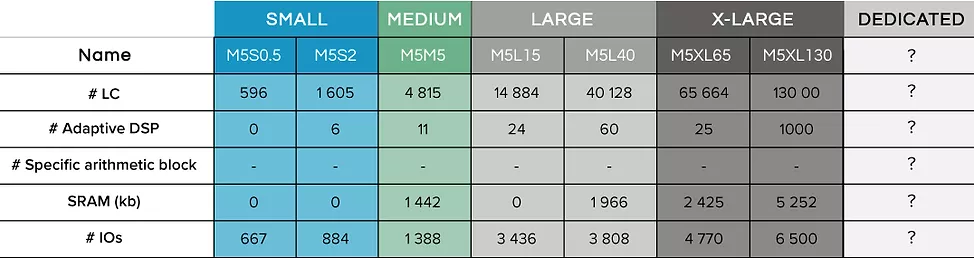

Menta eFPGA IP Cores are organized in families based on the number of Logic Cells (LC) available:

SMALL

for 100 to 2K LC

MED

for 2K to 6K LC

LARGE

for 6K to 60K LC

EXTRA LARGE

for 60K to 200K LC

This table provides examples of eFPGA that can be provided. Every element of the eFPGA can be defined in numbers: logic cells, adaptive DSP, SRAM (type and amount) and IOs.