Semiconductor Process and Device Simulation

Benefits of TCAD

Reduce Development Costs

- Reduce the time and manufacturing cycles spent to develop semiconductor technologies

- ITRS roadmaps indicates that TCAD simulation can reduce the costs during development cycles by ~30%

Visualize Internal Physical Processes

Using simulation, you can see ‘inside” the device. Experimental measurements tell you what happens, but not why it happens. TCAD can tell you why. For example:

- Reverse voltage characterization on a power device tells you what happens at high reverse biases. The device experiences reverse breakdown at a specific voltage

- A TCAD simulation can also replicate the reverse current-voltage curve, but also can also tell you why the device is experiencing breakdown. In TCAD the engineer can “see inside” the device and identify what region within the semiconductor first succumbs to breakdown due to high impact ionization generation

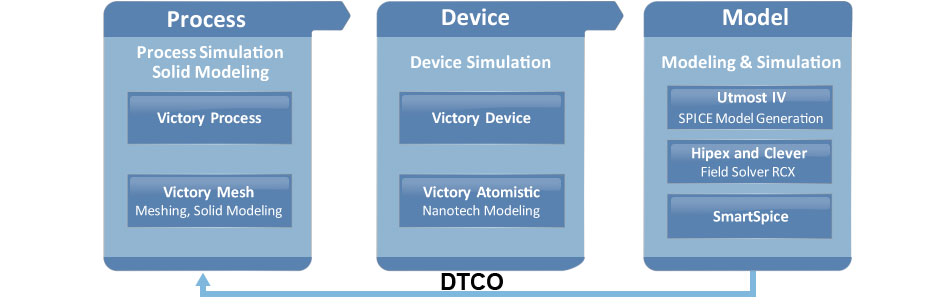

Design Technology Co-Optimization (DTCO)

- TCAD is part of a DTCO flow which improves designs across multiple domains – Layout, Process, Device, SPICE, and RC extraction

- A full TCAD to SPICE flow, in an integrated DTCO environment, delivers clear actionable results for circuit design optimization

Virtual Experimentation

- Experiment with cause and effect: Change the device design (layout), technology (semiconductor process steps) or device operation condition (biasing, etc) and understand and improve device performance

- Experiment with theories in TCAD: control the impact of various physics in the device via model settings and coefficients. If theory as applied to simulation matches the measured result, you may have found the root cause and gained physical understanding of device performance

Communicate Device Complexities Clearly

- Semiconductor device design, and processing of semiconductors is a complex task. Engineers must work collaboratively to solve problems, explain issues and opportunities to a variety of colleagues with varied technical expertise

- Utilizing TCAD can clearly communicate device and process changes; communicating potential performance improvements with clarity while minimizing manufacturing cycle times

TCAD Resources

VICTORYPROCESS : 3D Process Simulation Examples

VICTORYPROCESS2D : 1D/2D Process Simulation Examples

VICTORYSTRESS : 2D/3D Stress Simulation

DTCO Tool Flow – Single Run-Time Environment for Design Technology Co-Optimization

Optical Simulations – Light Emitting and Absorbing Devices

Power Device Solutions – Full TCAD to SPICE Flow

Parasitic Extraction – Full Chip and Cell Level RC Extraction

Process Simulation Options – Four Ways to Create a Physical Structure

Radiation Effects Module – Total Dose and Single Event Phenomenon, Damage Inducing and Elastic Interactions

Victory Atomistic – Practical Atomic-Scale Simulation

Interactive Tools – Pre and Post Processing Tools

Victory Device – Device Simulation VWF – Virtual Wafer Fab

Victory Process – Process Simulation

Clever – RC Extractor for Realistic 3D Structures

Victory Mesh – Meshing & Solid Modeling

Hipex – Full-chip Rule-based RC Parasitic Extraction

Solar Cells

MEMS

Memory Devices

Optoelectronics

Radiation, SEU and Reliability

Power Device Simulation

ESD Simulation

Organic Device Technology

Interconnect Simulation

SOI Technology

TFT Technology

Compound Devices

CMOS Technology

Process Simulation

Bipolar Technology

Simulation of AlGaInP Multiple Quantum Well LED for Micro Display

Relating Platinum Diffusion to Minority Carrier Lifetime Control in PiN Diode: Coupled TCAD Process and Device Simulation

Enabling the Rapid Development of SiC Superjunction-MOSFETs in Collaboration with mi2-factory

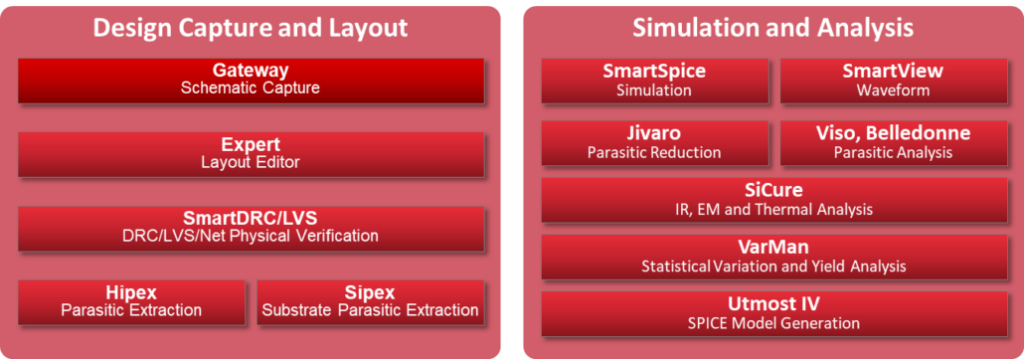

Full Analog IC-CAD Design Flow

Silvaco offer a full IC-CAD design flow including design capture, circuit simulation, layout design, physical verification, parasitic extraction and reduction, and post-layout analysis including statistical variation, IR, EM and Thermal analysis.

Schematic Editor

Gateway is a highly productive environment with intuitive editing, capacity to support large and complex hierarchical or flat designs, ability to automatically generate symbols from existing legacy netlists and support for industry standard netlist and interface formats. It features tight integrations to Silvaco TCAD and analog custom design tools.

Layout Editor

Expert is a hierarchical IC layout editor featuring high capacity and flexible use across many silicon technologies in analog, mixed-signal, RF and digital circuits. As a key part of Silvaco’s custom IC design suite, Expert is seamlessly integrated with Gateway schematic design and SmartDRC/LVS physical verification environments. Links to Calibre® RealTime provide sign-off quality DRC interactively and on demand. Expert’s intuitive interface, easy setup and interactive rule checking enable designers to quickly produce correct layouts resulting in fast tapeouts.

DRC/LVS Physical Verification

SmartDRC/LVS performs physical verification of analog, digital and mixed-signal ICs including design rule checks (DRC), layout connectivity extraction and layout vs schematic (LVS) comparison. Its unique architecture delivers high performance and capacity using multiple CPUs, accurate processing of complex shapes, and exceptional user productivity with fast interactive verification and intuitive debug.

Full-Chip Parasitic Extraction

Hipex provides an accurate and fast solution for the extraction of parasitic capacitance and resistance from hierarchical layouts of analog, mixed-signal, memory IC and SoC designs. As part of Silvaco’s complete Physical IC design Verification flow, it is tightly integrated with Expert layout editor for DRC/LVS and RC parasitic extraction. It supports both fast pattern matching and field-solver solver modes.

Substrate Parasitic Extraction

The development of RF Front-End Modules (FEM) — Low-Noise Amplifiers (LNAs), Power Amplifiers (PAs), and RF switches — for mmW and 5G applications can result in many silicon iterations, due to poor correlation between simulation and silicon measurements caused by substract effects. Sipex substrate parasitics extraction enables RF IC designers to model these effects accurately and easily with minimal impact on simulation times.

Analog Simulation

SmartSpice is a high performance parallel SPICE simulator that provides a complete set of active device models, Verilog-A compact modeling, tight integration with the schematic, layout and TCAD analysis tools. It is a proven, comprehensive solution for applications including simulation of complex high precision analog and mixed-signal circuits, memory, custom digital design and characterizing cell libraries of advanced semiconductor processes.

Parasitic Reduction and Analysis

Jivaro is a netlist reduction platform. It speeds up the simulation time, increases accuracy and also reduces memory footprint during simulation. Viso analyses netlist parasitics to explore delay, resistance and capacitance values for quick debug post-layout design problems. Belledonne and Brenner are used for layout comparison of extracted netlists to qualify layout parasitic extraction (LPE) flows.

Reliability Analysis

SiCure is a power integrity, EM, IR and Thermal analysis tool, with built-in SmartSpice, for analog and mixed-signal IC designs. SiCure’s patented multi-analysis engines ensure that interactions among the different domains are correctly integrated to give a high accuracy result.

Variation Analysis

VarMan is a comprehensive suite of analysis tools that allow designers to accurately address statistical variations and to make the right implementation decision upfront. VarMan is a new-generation tool that employs machine-learning technology and provides efficient and reliable solutions for analog, RF, standard cells, IO, and memory designs.

SPICE Model Generation

CDT is the industry’s premier solution to address these challenges for the characterization and modeling of cutting-edge CMOS and compound semiconductor devices. It provides an easy-to-use, database-driven environment for the characterization of semiconductor devices and the generation of accurate, high-quality SPICE models, macro-models and Verilog-A models for analog, mixed-signal and RF applications.

Analog Custom Design Resources

Analog Custom Design and Analysis

SmartSpice

Gateway

Model Generation

Guardian DRC

Utmost IV

Guardian LVS

Parasitic Extraction

Expert

Hipex

SmartSpice: Built-in Interconnect RC Network Reduction

Managing Circuit Simulation Using VWF

SmartSpice Circuit Design Using Local and Global Optimization

Interactive Measurement in SmartView

Performing Operation Point Analyses with Variable Sweeps

Simulating Circuits with Parasitics and RCL Reduction

Schematic Driven Process Corners Analysis

| Gateway – Schematic Capture | Jivaro– Parasitic Reduction for Fast, Accurate Simulation |

| Expert – Layout Editor | Viso – Parasitic Analyzer and Debugger |

| Guardian – DRC/LVS/Net Physical Verification | Belledonne – Layout Parastic Extraction Comparison |

| SmartSpice – Circuit Simulator | VarMan – Statistical Variation and Yield Analyzer |

| SmartView – Waveform Analyzer | VarMan XMA Option – Full-chip RAM Yield Analyzer |

| SmartSpice RadHard – Radiation Effects Circuit Simulator | VarMan for Libraries – Library Statistical Functional Verification |

| SmartSpice Pro– FastSPICE Simulator | Utmost IV– Device Characterization and SPICE Modeling |

| Hipex – Full-Chip Parasitic Extraction | Utmost IV Quick-Start– Model extraction and Optimization Templates |

| SiCure – EM, IR, Thermal Analysis | TechModeler – Verilog-A Blackbox Device Modeling |

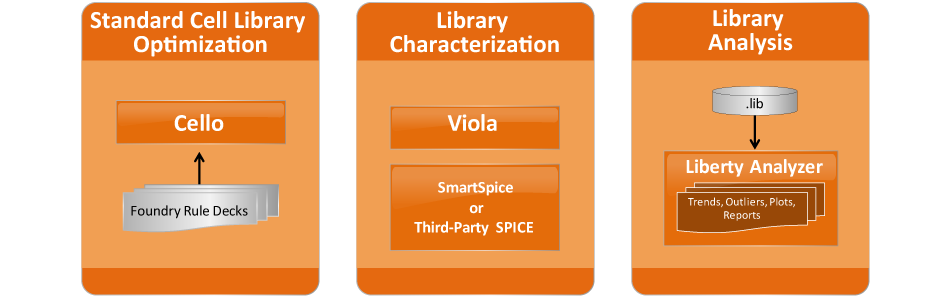

Overview

The Silvaco Library Platform is the most comprehensive tool suite for efficient creation and validation of digital cell libraries. It is engineered to support libraries containing thousands of cells.

Library Creation, Migration and Optimization

Cello is the industry’s most versatile, integrated and easy-to-use solution for digital cell library creation, optimization and process migration. It enables designers of digital CMOS ICs to custom-tailor digital cell libraries and explore the impact of alternate device models, design rules and cell architectures.

Library Characterization

Viola is a unique, all-inclusive package for fast and accurate characterization of digital cell libraries. The package includes a powerful SPICE-based characterization engine with fully automated stimulus generation, a library model checker and a databook generator.

Liberty File Analysis

Liberty Analyzer displays, analyzes, compares and validates Liberty™ files for timing, power, noise and area. Liberty Analyzer handles multiple NLDM, NLPM, CCS and ECSM models at library, cell, pin and individual arc levels while providing insightful statistical data. It displays and plots relative and absolute differences with configurable thresholds for easy spotting of trends and outliers. Its validation routines include a sanity check that validates libraries for use with any design flow.

Resources

- Cello – Cell Library Creation, Migration and Optimization

- Viola – Cell Library Characterization, Validation and Variation Modeling

- Liberty Analyzer

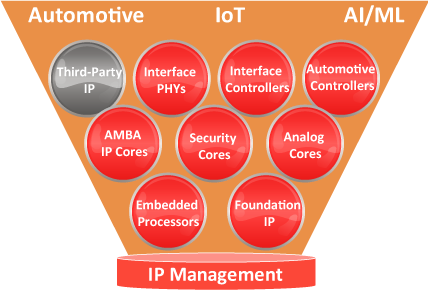

Silvaco IP products and solutions include embedded processors, wired interfaces, bus fabrics, peripheral controllers, and cores for automotive, consumer and IoT/sensor applications. Samsung Foundry design IP is now licensed and supported by Silvaco. This catalog of IP meets the requirements for different consumer, mobile, and HPC applications including wired and high-speed interfaces, analog and mixed-signal blocks.

Link – www.silvaco.com